LIQID CDI CXLソリューション製品概要(2)メモリ実装革命?

LIQID CDI CXLソリューション製品概要(2)メモリ実装革命?

前回のコラムでは、CXL2.0対応製品がLIQID社から発表されたことにちなんで、製品の基礎技術になっているCXLについて概観し、その出自や業界動向、各社からリリースされている対応製品などを紹介しました。

今回は、CXLが提唱するメモリの新しい実装方法についてご覧いただいた後、LIQID CDI CXL2.0対応製品がそれらをどのようにインプリメントしているかについて概要をご紹介したいと思います。

1. CXLにより広がるメモリ実装方法の選択肢

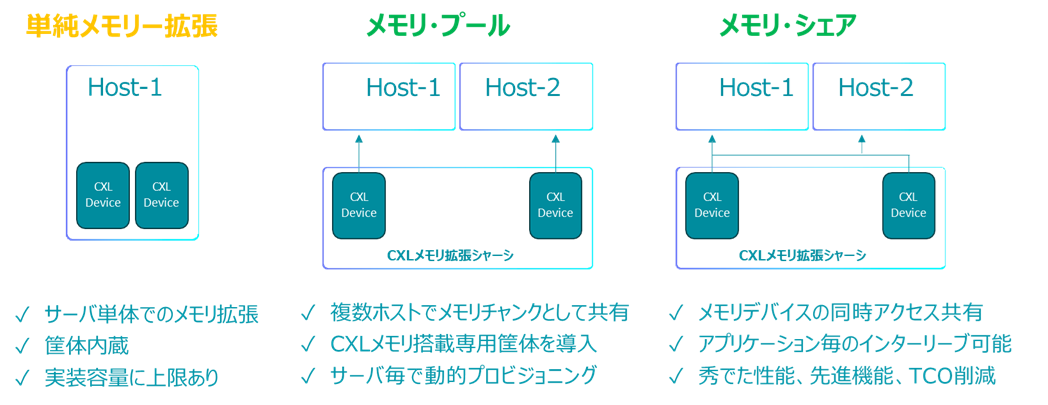

前回のコラムと一部重複しますが、CXLメモリは従来のマザーボード上のメモリスロットではなく、PCIeインタフェースを介して実装するメモリです。CXL標準では、下図のような三つのメモリ実装方法が想定されています。

Ⅰ. 単純メモリ拡張

ホスト・サーバ単体のメモリ容量を拡張する方法です。CXLメモリをサーバ筐体内部に直接実装するか、CXLメモリを専用筐体のようなシャーシに搭載しPCIeファブリックネットワークを介してホスト・サーバと接続する方法があります。

Ⅱ. メモリ・プール

複数のホスト・サーバ間でCXLメモリを共有(タイムシェア)する方法です。CXLメモリの容量をブロック(チャンク)化して、その単位で各ホストに割り当てます。基本的に、ホスト間で同時に同じメモリ・ブロック(チャンク)を共有することはしません。

ホスト・サーバとCXLメモリ(が搭載されている専用筐体)の間はPCIeファブリックネットワークで接続します。

Ⅲ. メモリ・シェア

上のメモリ・プールと似ていますが、こちらはタイムシェアではなくメモリ領域のデータを複数のホスト・サーバで共有する方法です。ホストとCXLメモリの接続方法(トポロジー)はプールと基本的に同じです。

2. LIQID CDI CXL2.0対応製品によるメモリ実装の実例

上図で簡単に示した新しいメモリ(CXLメモリ)実装方法がLIQID製品ではどのようにインプリメントされるのか、実製品構成に倣って説明いたします。

その前に、LIQID CDI CXL対応製品のベースとなっているLIQID CDI(コンポーザブル・ディスアグリゲーテッド・インフラストラクチャ)製品について簡単におさらいしておきます。

番外#1) おさらい:LIQID CDI製品(コンセプト)

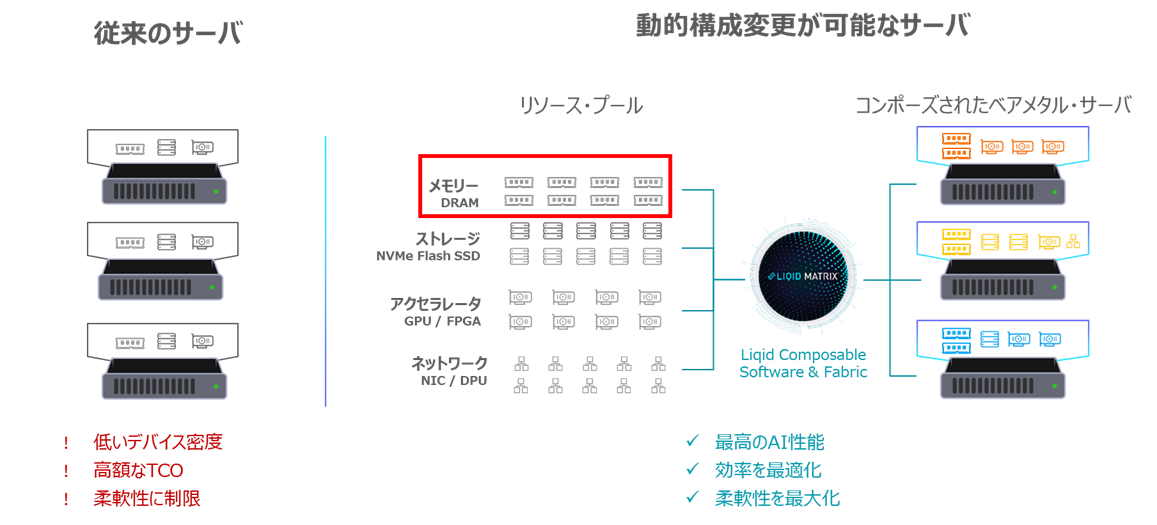

LIQID CDI製品とは、GPUなどのPCIeデバイスをLIQID社専用筐体(拡張シャーシ)に導入し(プール化)、PCIeファブリック・ネットワークを介して接続した複数のホスト間で共有(タイムシェア)できるようにする技術製品です。

以下の概念図が示しているのは、従来のベアメタルサーバとLIQID CDIシステムを構成するベアメタルサーバの比較です。

従来のベアメタルサーバはその内部にGPUやNIC, SSDなどのPCIeデバイスを導入します。LIQID CDIでは、PCIeデバイスを外部の専用シャーシに導入し、ホスト(ベアメタルサーバ)間で共有できるようにプール化します。専用シャーシはPCIeファブリック・スイッチを介してホストに接続されます。LIQID Matrix CDI管理ソフトウェアを操作することで、必要なPCIeデバイスを必要な数だけ専用シャーシ内のデバイス・プールからホストに割り当て、所望の仕様のベアメタルサーバを動的に構成することができます(コンポーズすると言います)。構成したベアメタルサーバの使用が済んだら、コンポーズしていたPCIeデバイスを他のユーザーが使用できるようにプールに返却します。

従来のサーバでは、内部の物理的な制約により搭載できるPCIeデバイスの数や構成(例えば異機種混在)に制限があったりしますが、LIQID CDIシステムではそのような制約はありません。一例ですが、1Uサーバ一台に30枚のGPUをコンポーズすることもでき、従来のサーバでは不可能なGPU密度を実現することが可能です。

今回LIQID社が発表したCXL2.0対応製品は、極単純化して言うと、このLIQID CDIシステムのPCIeデバイス・プールにCXLメモリを追加してコンポーズ対象にすることを可能にした製品と言えます。

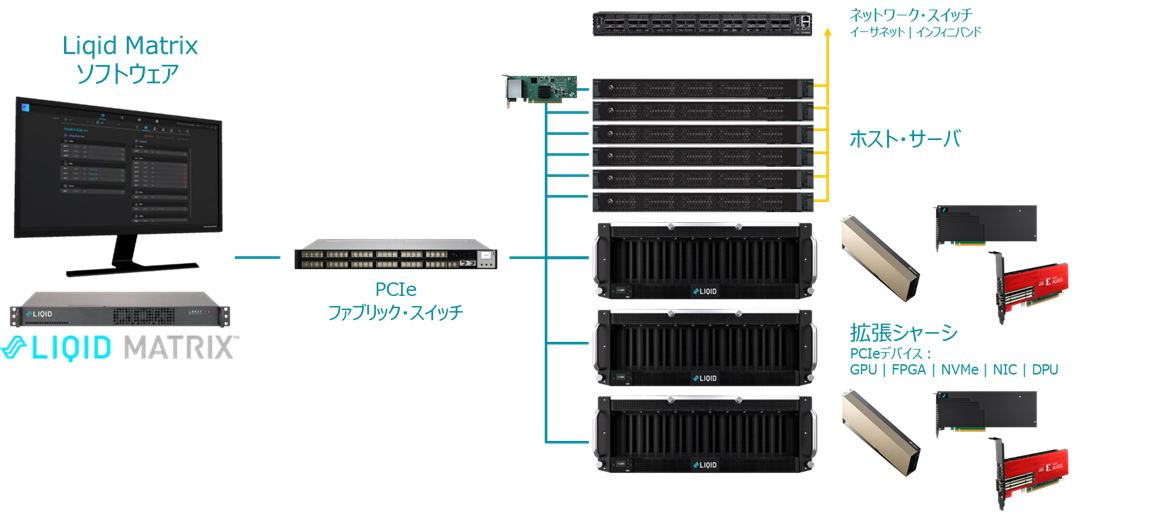

番外#2) おさらい:LIQID CDI製品(構成機器)

LIQID CDI製品は下図のような機器で構成されます

LIQID CDI製品構成機器:

a) Matrixソフトウエア:CDIのすべてを司る管理ソフトウェア(専用Director上で動作)

b) PCIeファブリック・スイッチ:ホストと拡張シャーシを接続するためのスイッチ

c) 拡張シャーシ:GPUなどPCIeデバイスを導入するためのシャーシ

d) HBA(ホストバスアダプター):ホストに搭載してPCIeファブリックに接続するためのHBA

※システム構成要素としてはCXL2.0対応製品もほぼ同様です(但し、論理的にはPCIeファブリックとCXLファブリックの違いがありますが、詳しくは次回以降のコラムで説明いたします。)

LIQID CXL製品のコンセプト・ベースともなるLIQID CDI製品のおさらいをしたところで、CXLによる新しいメモリ実装方法を同社CXL製品がどのように実現しているか見て行きたいと思います。

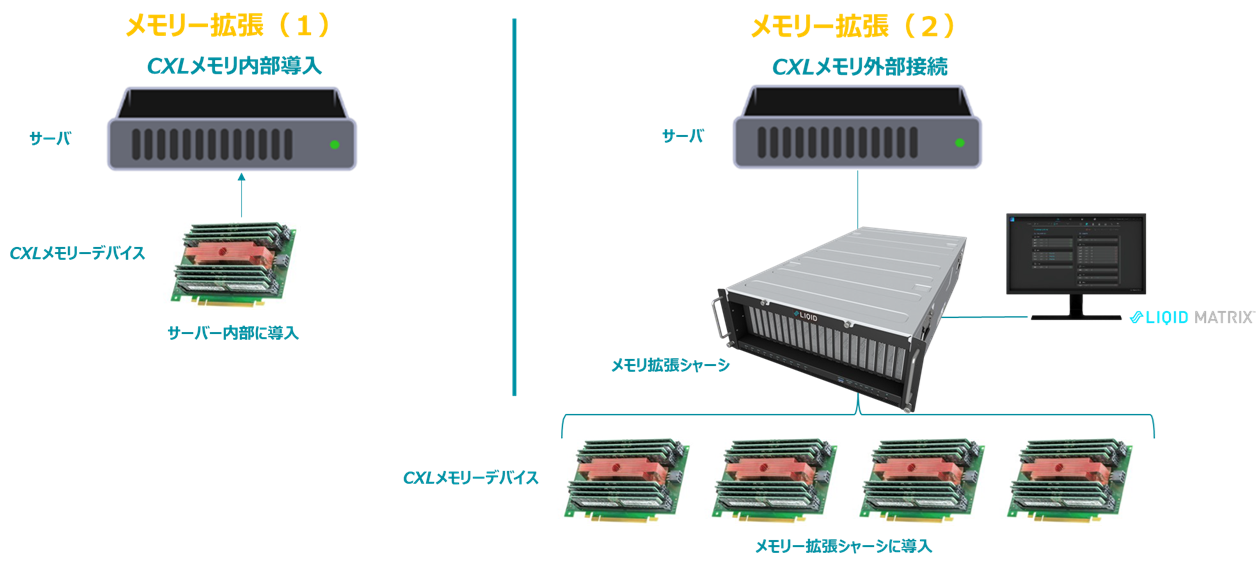

Ⅰ. LIQID CXL製品による「単純メモリ拡張」

前項で紹介したメモリの実装方法「単純メモリ拡張」はLIQID CXL製品を用いると下図のようになります。

左側はCXLメモリデバイスをホスト・サーバ内部に導入する場合です。右側はホスト・サーバ内部にCXLメモリを導入するのではなく、別に用意したメモリ拡張シャーシにCXLメモリを導入し、CXLファブリック(物理層はPCIe)を介してホスト・サーバと接続する場合です。このメモリ拡張シャーシを使用する場合、ホスト・サーバ内部の従来のDIMM容量に加えて、最大20TBのCXLメモリを実装することが可能です。

Ⅱ. LIQID CXL製品による「メモリ・プール」

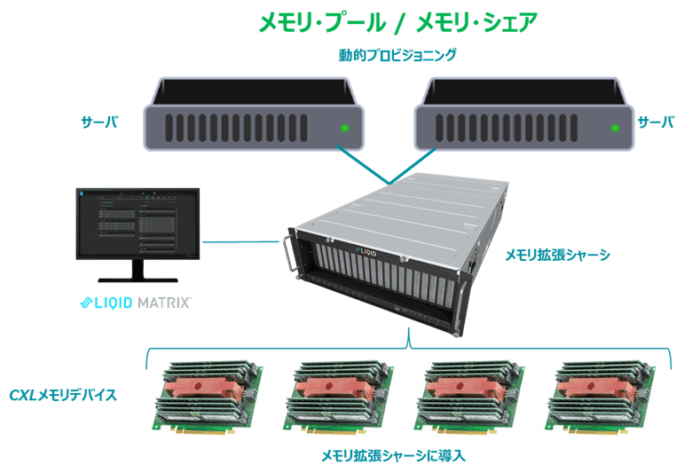

同じく前項で紹介した「メモリ・プール」のLIQID製品による実現概念図を以下に示します。

メモリ拡張シャーシには、PCIeスイッチコントローラが内蔵されており、そのホストポートを介してホスト・サーバとCXLファブリック(PCIe物理層)接続します。

メモリ拡張シャーシは最大20TBのCXLメモリを搭載することが可能で、これらのCXLメモリをLIQID Matrix管理ソフトウェアにより一定のサイズのチャンクにブロック化して、ホスト・サーバに割り当て可能にします。「メモリ・プール」は、このブロック化されたチャンクの集合体です。個々のメモリ・ブロックは一時点で一台のホスト・サーバにのみ割り当てられ、使用後は再びプールに戻すことで再利用可能になります。

Ⅲ. LIQID CDI CXL製品による「メモリ・シェア」

前項の「メモリ・プール」とシステムのトポロジーは類似です。複数のホストがCXLファブリック(PCIe物理層)を介してCXLメモリを搭載しているメモリ拡張シャーシに接続されます(「メモリ・プール」と実現概念図共有)。

「メモリ・シェア」が「メモリ・プール」と大きく異なる点は、同じメモリ領域(同じメモリアドレス領域)にストアされているデータを、複数のホストが直接共有・アクセスすることができるという点です。もちろんデータのコヒーレンシを担保しなければなりませんので、CXL2.0世代では別途ファイルシステムを被せるなどの工夫をしたデプロイが必要になります。

「メモリ・プール」、「メモリ・シェア」の共有型のメモリ実装方法は、異なるホスト・サーバ上のCPU間だけではなく、GPUとCPU間、GPUとGPU間などのデータ共有にも今後道が開かれていくことが期待されています。

今回のコラムでは、CXLが広げるメモリ実装方法のバリエーションをご紹介し、それらがLIQID CDI CXL2.0対応製品でどのように実現するのか概要をお伝えしました。

次回は、LIQID CDI CXL2.0対応製品が実アプリケーションでどのような効果をもたらすのか、今後期待される課題解決の可能性と合わせてご紹介する予定です。

(MF)